|

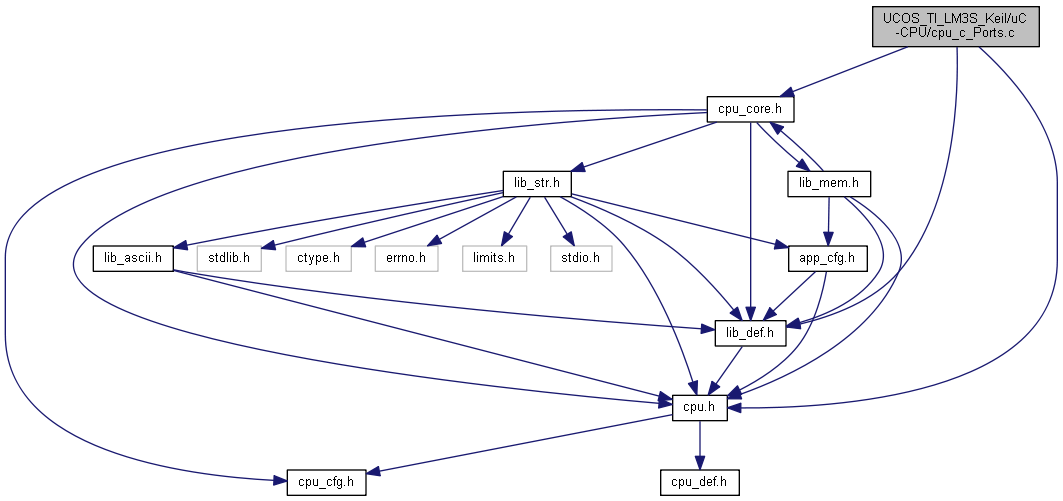

UCOS_TI_LM3S_Keil

|

|

UCOS_TI_LM3S_Keil

|

宏定义 | |

| #define | CPU_INT_SRC_POS_MAX ((((CPU_REG_NVIC_NVIC + 1) & 0x1F) * 32) + 16) |

| #define | CPU_BIT_BAND_SRAM_REG_LO 0x20000000 |

| #define | CPU_BIT_BAND_SRAM_REG_HI 0x200FFFFF |

| #define | CPU_BIT_BAND_SRAM_BASE 0x22000000 |

| #define | CPU_BIT_BAND_PERIPH_REG_LO 0x40000000 |

| #define | CPU_BIT_BAND_PERIPH_REG_HI 0x400FFFFF |

| #define | CPU_BIT_BAND_PERIPH_BASE 0x42000000 |

函数 | |

| void | CPU_BitBandClr (CPU_ADDR addr, CPU_INT08U bit_nbr) |

| void | CPU_BitBandSet (CPU_ADDR addr, CPU_INT08U bit_nbr) |

| void | CPU_IntSrcDis (CPU_INT08U pos) |

| void | CPU_IntSrcEn (CPU_INT08U pos) |

| void | CPU_IntSrcPrioSet (CPU_INT08U pos, CPU_INT08U prio) |

| CPU_INT16S | CPU_IntSrcPrioGet (CPU_INT08U pos) |

| #define CPU_INT_SRC_POS_MAX ((((CPU_REG_NVIC_NVIC + 1) & 0x1F) * 32) + 16) |

在文件 cpu_c_Ports.c 第 59 行定义.

参考自 CPU_IntSrcDis(), CPU_IntSrcEn(), CPU_IntSrcPrioGet() , 以及 CPU_IntSrcPrioSet().

| #define CPU_BIT_BAND_SRAM_REG_LO 0x20000000 |

在文件 cpu_c_Ports.c 第 61 行定义.

参考自 CPU_BitBandClr() , 以及 CPU_BitBandSet().

| #define CPU_BIT_BAND_SRAM_REG_HI 0x200FFFFF |

在文件 cpu_c_Ports.c 第 62 行定义.

参考自 CPU_BitBandClr() , 以及 CPU_BitBandSet().

| #define CPU_BIT_BAND_SRAM_BASE 0x22000000 |

在文件 cpu_c_Ports.c 第 63 行定义.

参考自 CPU_BitBandClr() , 以及 CPU_BitBandSet().

| #define CPU_BIT_BAND_PERIPH_REG_LO 0x40000000 |

在文件 cpu_c_Ports.c 第 66 行定义.

参考自 CPU_BitBandClr() , 以及 CPU_BitBandSet().

| #define CPU_BIT_BAND_PERIPH_REG_HI 0x400FFFFF |

在文件 cpu_c_Ports.c 第 67 行定义.

参考自 CPU_BitBandClr() , 以及 CPU_BitBandSet().

| #define CPU_BIT_BAND_PERIPH_BASE 0x42000000 |

在文件 cpu_c_Ports.c 第 68 行定义.

参考自 CPU_BitBandClr() , 以及 CPU_BitBandSet().

| void CPU_BitBandClr | ( | CPU_ADDR | addr, |

| CPU_INT08U | bit_nbr | ||

| ) |

| void CPU_BitBandSet | ( | CPU_ADDR | addr, |

| CPU_INT08U | bit_nbr | ||

| ) |

| void CPU_IntSrcDis | ( | CPU_INT08U | pos) |

在文件 cpu_c_Ports.c 第 249 行定义.

参考 CPU_CRITICAL_ENTER, CPU_CRITICAL_EXIT, CPU_INT_BUSFAULT, CPU_INT_DBGMON, CPU_INT_HFAULT, CPU_INT_MEM, CPU_INT_NMI, CPU_INT_PENDSV, CPU_INT_RESET, CPU_INT_RSVD_07, CPU_INT_RSVD_08, CPU_INT_RSVD_09, CPU_INT_RSVD_10, CPU_INT_RSVD_13, CPU_INT_SRC_POS_MAX, CPU_INT_STK_PTR, CPU_INT_SVCALL, CPU_INT_SYSTICK, CPU_INT_USAGEFAULT, CPU_REG_NVIC_CLREN, CPU_REG_NVIC_SHCSR, CPU_REG_NVIC_SHCSR_BUSFAULTENA, CPU_REG_NVIC_SHCSR_MEMFAULTENA, CPU_REG_NVIC_SHCSR_USGFAULTENA, CPU_REG_NVIC_ST_CTRL, CPU_REG_NVIC_ST_CTRL_ENABLE, CPU_SR_ALLOC , 以及 DEF_BIT.

参考自 BSP_IntDis().

| void CPU_IntSrcEn | ( | CPU_INT08U | pos) |

在文件 cpu_c_Ports.c 第 338 行定义.

参考 CPU_CRITICAL_ENTER, CPU_CRITICAL_EXIT, CPU_INT_BUSFAULT, CPU_INT_DBGMON, CPU_INT_HFAULT, CPU_INT_MEM, CPU_INT_NMI, CPU_INT_PENDSV, CPU_INT_RESET, CPU_INT_RSVD_07, CPU_INT_RSVD_08, CPU_INT_RSVD_09, CPU_INT_RSVD_10, CPU_INT_RSVD_13, CPU_INT_SRC_POS_MAX, CPU_INT_STK_PTR, CPU_INT_SVCALL, CPU_INT_SYSTICK, CPU_INT_USAGEFAULT, CPU_REG_NVIC_SETEN, CPU_REG_NVIC_SHCSR, CPU_REG_NVIC_SHCSR_BUSFAULTENA, CPU_REG_NVIC_SHCSR_MEMFAULTENA, CPU_REG_NVIC_SHCSR_USGFAULTENA, CPU_REG_NVIC_ST_CTRL, CPU_REG_NVIC_ST_CTRL_ENABLE, CPU_SR_ALLOC , 以及 DEF_BIT.

参考自 BSP_IntEn().

| void CPU_IntSrcPrioSet | ( | CPU_INT08U | pos, |

| CPU_INT08U | prio | ||

| ) |

在文件 cpu_c_Ports.c 第 433 行定义.

参考 CPU_CRITICAL_ENTER, CPU_CRITICAL_EXIT, CPU_INT_BUSFAULT, CPU_INT_DBGMON, CPU_INT_HFAULT, CPU_INT_MEM, CPU_INT_NMI, CPU_INT_PENDSV, CPU_INT_RESET, CPU_INT_RSVD_07, CPU_INT_RSVD_08, CPU_INT_RSVD_09, CPU_INT_RSVD_10, CPU_INT_RSVD_13, CPU_INT_SRC_POS_MAX, CPU_INT_STK_PTR, CPU_INT_SVCALL, CPU_INT_SYSTICK, CPU_INT_USAGEFAULT, CPU_REG_NVIC_PRIO, CPU_REG_NVIC_SHPRI1, CPU_REG_NVIC_SHPRI2, CPU_REG_NVIC_SHPRI3, CPU_RevBits(), CPU_SR_ALLOC, DEF_OCTET_MASK , 以及 DEF_OCTET_NBR_BITS.

参考自 BSP_IntPrioSet().

| CPU_INT16S CPU_IntSrcPrioGet | ( | CPU_INT08U | pos) |

在文件 cpu_c_Ports.c 第 568 行定义.

参考 CPU_CRITICAL_ENTER, CPU_CRITICAL_EXIT, CPU_INT_BUSFAULT, CPU_INT_DBGMON, CPU_INT_HFAULT, CPU_INT_MEM, CPU_INT_NMI, CPU_INT_PENDSV, CPU_INT_RESET, CPU_INT_RSVD_07, CPU_INT_RSVD_08, CPU_INT_RSVD_09, CPU_INT_RSVD_10, CPU_INT_RSVD_13, CPU_INT_SRC_POS_MAX, CPU_INT_STK_PTR, CPU_INT_SVCALL, CPU_INT_SYSTICK, CPU_INT_USAGEFAULT, CPU_REG_NVIC_PRIO, CPU_REG_NVIC_SHPRI1, CPU_REG_NVIC_SHPRI2, CPU_REG_NVIC_SHPRI3, CPU_RevBits(), CPU_SR_ALLOC, DEF_INT_16S_MIN_VAL, DEF_OCTET_MASK , 以及 DEF_OCTET_NBR_BITS.